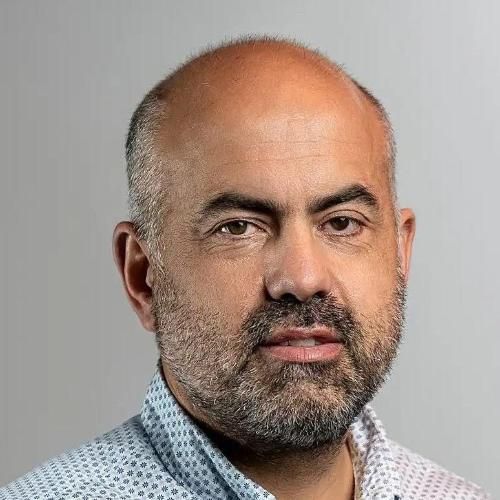

ANTONIO JESUS

GARCIA LOUREIRO

Catedrático de universidad

DANIEL

NAGY

Profesor ayudante doctor

Publicaciones en las que colabora con DANIEL NAGY (29)

2024

-

Scaling Challenges of Nanosheet Field-Effect Transistors into Sub-2 nm Nodes

IEEE Journal of the Electron Devices Society, Vol. 12, pp. 479-485

2020

-

Benchmarking of FinFET, Nanosheet, and Nanowire FET Architectures for Future Technology Nodes

IEEE Access, Vol. 8, pp. 53196-53202

2019

-

A multi-method simulation toolbox to study performance and variability of nanowire FETs

Materials, Vol. 12, Núm. 15

-

Drift-Diffusion Versus Monte Carlo Simulated ON-Current Variability in Nanowire FETs

IEEE Access, Vol. 7, pp. 12790-12797

-

Impact of gate edge roughness variability on FinFET and gate-all-around nanowire FET

IEEE Electron Device Letters, Vol. 40, Núm. 4, pp. 510-513

-

Impact of threshold voltage extraction methods on semiconductor device variability

Solid-State Electronics, Vol. 159, pp. 165-170

2018

-

FinFET versus gate-all-around nanowire FET: Performance, scaling, and variability

IEEE Journal of the Electron Devices Society, Vol. 6, Núm. 1, pp. 332-340

-

FoMPy: A figure of merit extraction tool for semiconductor device simulations

2018 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon, EUROSOI-ULIS 2018

-

Impact of Cross-Sectional Shape on 10-nm Gate Length InGaAs FinFET Performance and Variability

IEEE Transactions on Electron Devices, Vol. 65, Núm. 2, pp. 456-462

-

Modelling of nanoscale multi-gate transistors affected by atomistic interface roughness

Journal of Physics Condensed Matter, Vol. 30, Núm. 14

2017

-

Metal Grain Granularity Study on a Gate-All-Around Nanowire FET

IEEE Transactions on Electron Devices, Vol. 64, Núm. 12, pp. 5263-5269

-

Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations

Solid-State Electronics, Vol. 128, pp. 17-24

-

Study of Strained Effects in Nanoscale GAA Nanowire FETs Using 3D Monte Carlo Simulations

2017 47TH EUROPEAN SOLID-STATE DEVICE RESEARCH CONFERENCE (ESSDERC)

-

Study of strained effects in nanoscale GAA nanowire FETs using 3D Monte Carlo simulations

European Solid-State Device Research Conference

2016

-

3D MC Simulations of Strain, Channel Orientation, and Quantum Confinement Effects in Nanoscale Si SOI FinFETs

2016 INTERNATIONAL CONFERENCE ON SIMULATION OF SEMICONDUCTOR PROCESSES AND DEVICES (SISPAD)

-

3D MC simulations of strain, channel orientation, and quantum confinement effects in nanoscale Si SOI FinFETs

International Conference on Simulation of Semiconductor Processes and Devices, SISPAD

-

Anisotropic Quantum Corrections for 3-D Finite-Element Monte Carlo Simulations of Nanoscale Multigate Transistors

IEEE Transactions on Electron Devices, Vol. 63, Núm. 3, pp. 933-939

-

Comparison of Fin-Edge Roughness and Metal Grain Work Function Variability in InGaAs and Si FinFETs

IEEE Transactions on Electron Devices, Vol. 63, Núm. 3, pp. 1209-1216

-

Scaling/LER study of Si GAA nanowire FET using 3D Finite Element Monte Carlo simulations

2016 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon, EUROSOI-ULIS 2016

-

Simulation study of scaled In0.53Ga0.47As and Si FinFETs for sub-16 nm technology nodes

Semiconductor Science and Technology, Vol. 31, Núm. 7