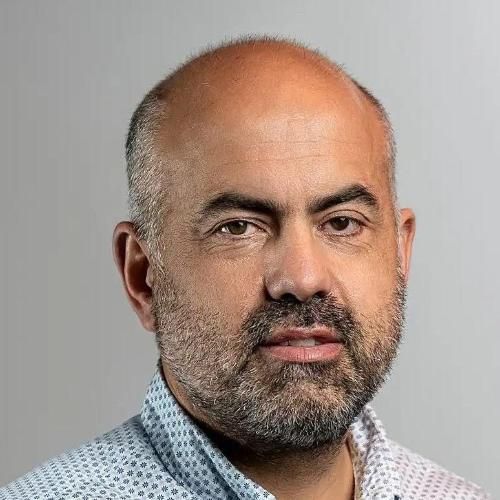

ANTONIO JESUS

GARCIA LOUREIRO

Catedrático de universidad

GUILLERMO

INDALECIO FERNANDEZ

Investigador en el periodo 2017-2019

Publicaciones en las que colabora con GUILLERMO INDALECIO FERNANDEZ (39)

2020

-

Benchmarking of FinFET, Nanosheet, and Nanowire FET Architectures for Future Technology Nodes

IEEE Access, Vol. 8, pp. 53196-53202

2019

-

A multi-method simulation toolbox to study performance and variability of nanowire FETs

Materials, Vol. 12, Núm. 15

-

AXC: A new format to perform the SpMV oriented to Intel Xeon Phi architecture in OpenCL

Concurrency Computation , Vol. 31, Núm. 1

-

Drift-Diffusion Versus Monte Carlo Simulated ON-Current Variability in Nanowire FETs

IEEE Access, Vol. 7, pp. 12790-12797

-

Impact of gate edge roughness variability on FinFET and gate-all-around nanowire FET

IEEE Electron Device Letters, Vol. 40, Núm. 4, pp. 510-513

-

Impact of threshold voltage extraction methods on semiconductor device variability

Solid-State Electronics, Vol. 159, pp. 165-170

2018

-

Analysis of Fluctuation Sensitivity Map Algorithms Applied to a 10nm GAA NW FET

Proceedings of the 2018 12th Spanish Conference on Electron Devices, CDE 2018

-

FinFET versus gate-all-around nanowire FET: Performance, scaling, and variability

IEEE Journal of the Electron Devices Society, Vol. 6, Núm. 1, pp. 332-340

-

FoMPy: A figure of merit extraction tool for semiconductor device simulations

2018 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon, EUROSOI-ULIS 2018

-

Impact of Cross-Sectional Shape on 10-nm Gate Length InGaAs FinFET Performance and Variability

IEEE Transactions on Electron Devices, Vol. 65, Núm. 2, pp. 456-462

-

Improving performance of iterative solvers with the AXC format using the Intel Xeon Phi

Journal of Supercomputing, Vol. 74, Núm. 6, pp. 2823-2840

-

MPI-Performance-Aware-Reallocation: method to optimize the mapping of processes applied to a cloud infrastructure

Computing, Vol. 100, Núm. 2, pp. 211-226

-

Spatial Sensitivity of Silicon GAA Nanowire FETs under Line Edge Roughness Variations

IEEE Journal of the Electron Devices Society, Vol. 6, pp. 601-610

2017

-

Fluctuation Sensitivity Map: A Novel Technique to Characterise and Predict Device Behaviour Under Metal Grain Work-Function Variability Effects

IEEE Transactions on Electron Devices, Vol. 64, Núm. 4, pp. 1695-1701

-

Metal Grain Granularity Study on a Gate-All-Around Nanowire FET

IEEE Transactions on Electron Devices, Vol. 64, Núm. 12, pp. 5263-5269

-

Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations

Solid-State Electronics, Vol. 128, pp. 17-24

2016

-

Comparison of Fin-Edge Roughness and Metal Grain Work Function Variability in InGaAs and Si FinFETs

IEEE Transactions on Electron Devices, Vol. 63, Núm. 3, pp. 1209-1216

-

GWMEP: Task-Manageras-a-Service in Apache CloudStack

IEEE Internet Computing, Vol. 20, Núm. 2, pp. 42-49

-

Scaling/LER study of Si GAA nanowire FET using 3D Finite Element Monte Carlo simulations

2016 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon, EUROSOI-ULIS 2016

-

Simulation study of scaled In0.53Ga0.47As and Si FinFETs for sub-16 nm technology nodes

Semiconductor Science and Technology, Vol. 31, Núm. 7